Under the core strategy of "Chips Define Machine Perception", the company will continuously push the computing boundaries at the edge and end sides, providing global customers with high-end master intelligent computing SoCs.

-

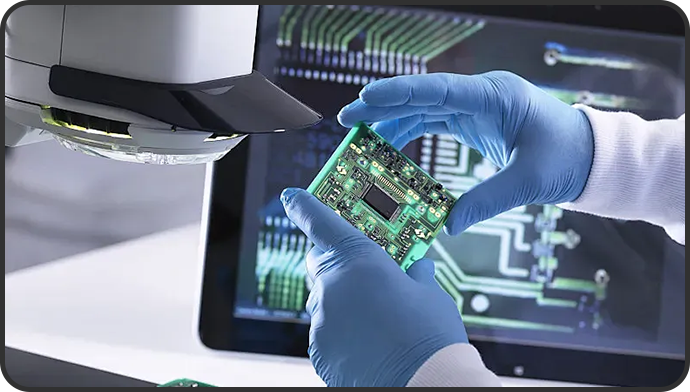

Full-Stack Technical Capabilities

Developed dynamic sparse computing architecture, improving energy efficiency ratio by more than 30%.

Created a full-link optimization toolchain featuring "chip-algorithm-scenario" collaboration, shortening customer development cycle by 50%.

Covers chip architecture design, algorithm optimization, and scenario-based SDK development, achieving deep integration between hardware and application scenarios.

-

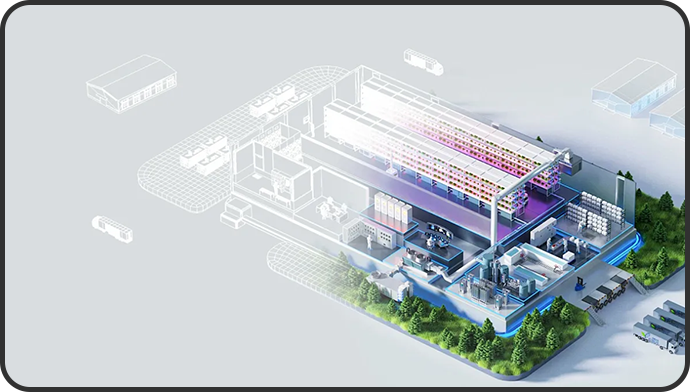

Vertical Domain Penetration

For high-frequency requirements such as object recognition, tracking and positioning, video slicing and image segmentation, dedicated acceleration engines (e.g., dynamic vision processing units) are provided.

-

Ecosystem Co-construction

Establish strategic cooperation with universities and laboratories, incubating 100+ scenario solutions.

Open hardware reference design (HDK) and algorithm model library to lower the barrier for secondary development.

Compatible with mainstream frameworks such as ROS, TensorFlow, etc., building a win-win system for developer community and partners.